# United States Patent [19]

# Steensgaard-Madsen

# [11] **Patent Number:** 5,982,317

# [45] **Date of Patent:** Nov. 9, 1999

# [54] OVERSAMPLED DIGITAL-TO-ANALOG CONVERTER BASED ON NONLINEAR SEPARATION AND LINEAR RECOMBINATION

[75] Inventor: Jesper Steensgaard-Madsen, 426 NW.

15<sup>th</sup> St. #1, Corvallis, Oreg. 97330

[73] Assignee: Jesper Steensgaard-Madsen, Hoejby

Sjaelland, Denmark

[21] Appl. No.: 09/061,671

[22] Filed: Apr. 16, 1998

## Related U.S. Application Data

[60] Provisional application No. 60/044,665, Apr. 18, 1997.

[51] Int. Cl.<sup>6</sup> ...... H03M 3/00

341/120, 144

## [56] References Cited

## U.S. PATENT DOCUMENTS

| 5,138,317 | 8/1992  | Story .                  |

|-----------|---------|--------------------------|

| 5,221,926 | 6/1993  | Jackson .                |

| 5,369,403 | 11/1994 | Temes et al              |

| 5,404,142 | 4/1995  | Adams et al              |

| 5,406,283 | 4/1995  | Leung 341/143            |

| 5,434,739 | 7/1995  | Norsworthy et al 341/143 |

| 5,648,779 | 7/1997  | Cabler 341/143           |

| 5,724,038 | 3/1998  | Koifman et al 341/144    |

|           |         |                          |

## OTHER PUBLICATIONS

"Delta-Sigma ADCs with Multibit Internal Converters," *Delta-Sigma Data Convertors; Theory, Design, and Simulation,* IEEE Press (1996), pp. 244–281.

"Linearity Enhancement of Multibit Delta–Sigma A/D and D/A Converters Using Data Weighted Averaging." *IEEE Transactions on Circuits and Systems–II: Analog And Digital Signal Processing*, vol. 42, No. 12 (1995), pp. 753–762.

"A Noise–Shaping Coder Topology for 15+ Bit Converters," *IEEE Journal of Solid–State Circuits*, vol. 24, No. 2 (1989), pp. 267–273.

"Multibit Sigma-Delta A/D Converter Incorporating A Novel Class of Dynamic Element Matching Techniques," *IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing*, vol. 39, No. 1 (1992), pp. 35–51. "Noise-Shaping D/A Converters for Delta-Sigma Modulation." *IEEE International Symposium on Circuits and Systems* (1996), pp. 441–444.

"Noise–shaped multibit D/A convertor employing unit elements," *IEEE Electronic Letters*, vol. 31, No. 20 (1995), pp. 1712–1713.

"A113dB SNR Oversampling DAC with Segmented Noise—Shaped Scrambling," 1998 *IEEE International Solid—State Circuits Conference*.

Primary Examiner—Howard L. Williams

Attorney, Agent, or Firm—Klarquist Sparkman Campbell Leigh & Whinston

#### [57] ABSTRACT

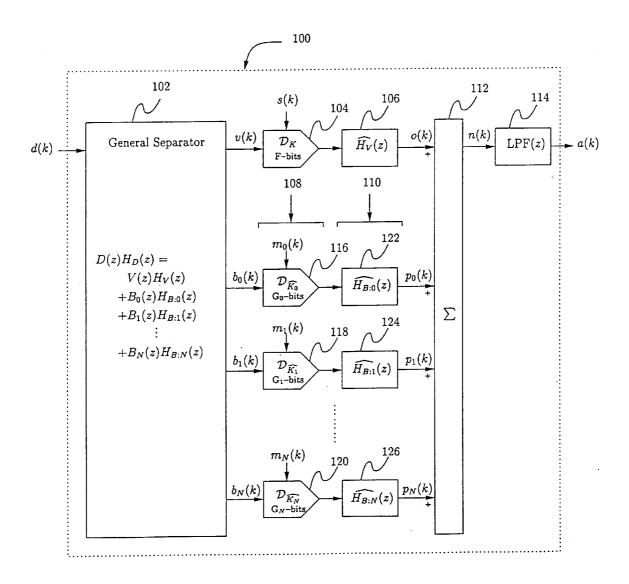

A error-shaping digital-to-analog (D/A) converter system [100], consisting of a separator [102], a set of D/A converters [104] [108], a set of optional analog filters [106] [108], a summation device [112], and an optional analog filter [114]. The separator [102] separates the digital input signal into a set of low-resolution signals of which only one has significant power in the system's signal band. These signals are D/A converted by mismatch-shaping D/A converters [104] [108], in some embodiments filtered by analog filters [106] [108], and then added by the summing device [112]. Imperfections of the employed D/A converters [104] [108] will only cause very small errors in the signal band, such errors being essentially uncorrelated to the digital input signal. The D/A converter system is comparable to a scaledelement D/A converter in which the distortion is transformed into a noise component having very little power in the signal band.

## 41 Claims, 12 Drawing Sheets

# Scaled Element D/A Converter

Figure 3 PRIOR ART

Figure 4 PRIOR ART

Figure 8 PRIOR ART

Figure 10

Figure 9

Figure 13

Figure 14

Figure 15

Figure 16

Figure 17

Figure 18

Figure 19

5,982,317

Figure 20

1

# OVERSAMPLED DIGITAL-TO-ANALOG CONVERTER BASED ON NONLINEAR SEPARATION AND LINEAR RECOMBINATION

## RELATED APPLICATION DATA

This application is based on and claims priority from U.S. Provisional Patent Application No. 60/044,665, filed Apr. 18, 1997.

#### BACKGROUND: FIELD OF INVENTION

The field of invention is data conversion, more precisely, this invention relates to oversampled mismatch-shaping digital-to-analog (D/A) data converters.

## BACKGROUND: DESCRIPTION OF PRIOR ART

To assure that the following description and discussion can be as exact as possible, D/A conversion will first be these definitions, the advantages and shortcomings of some prior-art D/A converters are discussed.

Definition of Digital-to-Analog Conversion

A D/A converter is a system which controls a physical phenomenon (the analog output) according to a digital input 25 signal.

The digital input signal will at any time be represented by codes  $D_i$  representing numbers  $d_i$ . The set of numbers  $\bigcup_i d_i$ , which can be represented, may be chosen arbitrarily; they do not necessarily have to be integers, uniformly spaced, nor 30 monotonic with respect to the index i.

The physical phenomenon, which the D/A converter controls, can be almost anything; it will often be a voltage, a current, a charge, a frequency, or a light intensity. This controlled physical phenomenon is, by an actual or a fictive 35 measurement, mapped to a real-number-valued variable a. The physical phenomenon is typically characterized by its measure a. The output of a D/A converter is thereby an "analog signal-carrying variable." A typical example is a D/A converter which controls the voltage between two 40 nodes; the output variable a is in that case "the output voltage.

The combination, that a is evaluated on a piecewise continuous scale and that it can be measured only at one physical location, makes it an "analog" signal. Digital 45 medium-resolution unit-element D/A converters have been signals, on the contrary, will have values from a finite set of possible values. In most implementations, digital signals are represented by a set of low-resolution signals; the bits in a digital data bus is an example.

digital signals will be referred to by their values d, rather than the codes  $D_i$  representing such values. From this point of view, a D/A converter can be thought of as a system that implements a function D mapping the input variable d to the characterized by:

$a=D(d)=K\cdot d$

K, the D/A converter's gain factor, is a dimensional constant 60 which fully characterizes the operation of an ideal D/A converter.

Many D/A converters are realized using a set of differently scaled D/A converters which in combination perform the D/A conversion. To facilitate a compact and clear 65 description of such D/A converters, the gain factor K of each converter will be used as an index to D. For example:

2

$a=D_{10}(d)=10\cdot d$

Definition of the Error Signal

All implementations of D/A converters are associated with some non-idealities. Non-idealities can be modeled by adding an error signal e to the ideal output:

$a=K\cdot d+e=V_K(d)+e$

In the general case, the error signal e will include both stochastic and deterministic errors. Stochastic errors are often referred to as "circuit noise," an issue which will not be addressed in the following discussion. It will be assumed 15 that all employed components are time-invariant; this implies that all signals in the discussed systems will be deterministic (non-stochastic) functions of the input. For delta-sigma D/A converters, the function describing e will be highly nonlinear and depend not only upon the instantadefined. Some terminology will also be defined. Based on 20 neous value of the input signal d, but upon the whole signal d since a reset event has taken place. In the following, the term "noise" refers to the deterministic part of the error signal e which is not harmonic distortion nor intermodulation of the input d.

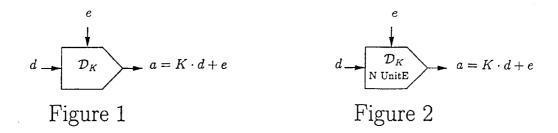

FIG. 1 shows the symbol which will be used in the drawings to illustrate a generic D/A converter.

Unit-Element D/A Converters

Unit-Element D/A converters are a very simple type of D/A converter. They require that the same analog signal (the unit element a<sub>unit</sub>) can be realized in multiple copies a<sub>unit:i</sub>. They also require that the unit elements can be accurately added in the analog domain.

The operation is straightforward. The ideal output must be expressible as an integer N times the ideal value of the unit element a<sub>unit</sub>. The output a is generated as the sum of the first N unit elements:  $a=a_{unit:1}+a_{unit:2}+\ldots+a_{unit:N}$ . The unit elements aunir: are ordered with respect to the index i, and the order is maintained throughout the period of operation. Addressing unit elements in this way is also known as "thermometer coding."

Unit-element D/A converters are not suitable for highresolution purposes; the thermometer coding becomes complex. However, because absolute monotonicity and a low differential nonlinearity (DNL) can be assured, some implemented. Techniques to ease the implementation of such converters are described in U.S. Pat. Nos. 5,539,405 and 5,600,319.

While unit-element D/A converters have a low DNL, their To aid the understanding of the following discussion, all 50 performance in terms of integral nonlinearity (INL) is only moderately good. Calibration techniques are required to obtain a total harmonic distortion (THD) of less than about

FIG. 2 shows the symbol which will be used in the output variable a. An ideal D/A converter can thereby be 55 drawings to illustrate a unit element D/A converter with N unit elements.

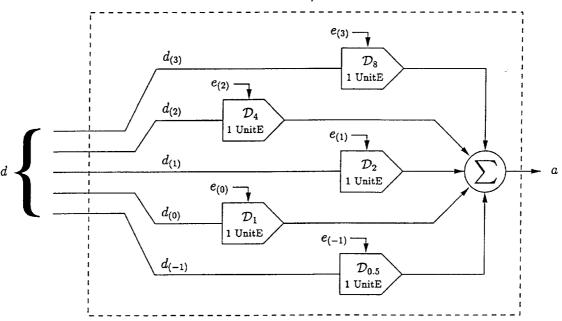

Scaled-Element D/A Converters

Medium-resolution medium-performance D/A converters are typically based on the number system in which the digital input d is coded.

Conventional Number Systems

The conventional number systems represent fractional numbers by ordered sets of digits. The represented number is a weighted sum of the digits representing it. Each digit's weight is determined by its position in the ordered set. For example, in the Arabic number system, the number 961.4 means 9 hundreds+6 tens+1 one+4 tenths.

A digital signal d, which is in the range 0–999.9 and has a step size of 0.1, can be represented by 4 digit signals:  $d_{(2)}$ ,  $d_{(1)}$ ,  $d_{(0)}$ , and  $d_{(-1)}$ . Each digit signal will at any given time have one value from the set  $\{0,1,2,3,4,5,6,7,8,9\}$ . The coding of each and all digit signals is uniquely defined by requiring the following equality to hold:

$$d = 10^2 d_{(2)} + 10^1 d_{(1)} + 10^0 d_{(0)} + 10^{-1} d_{(-1)}$$

Each digit signal has a non-linear relationship with d; 10 however, d is a linear function of the digit signals representing it. The linearity implies that the D/A conversion can be performed by D/A converting each digit signal separately and subsequently summing the scaled analog digit signals in the analog domain. In electronic circuits, digital signals are usually coded in the binary number system. In that case, the weights of the digit signals are powers of 2 (as opposed to the powers of 10 which are used in the Arabic number system). Each digit signal will either have the value 0 or 1. The internal D/A converters, which are used to convert the digit signals, can therefore be implemented by a single element scaled proportional to the respective digit signal's weight.

An example of a binary-scaled-element D/A converter is shown in FIG. 3; it has a range from 0 to 15.5 with a step 25 size of 0.5. According to the figure, the output-referred error signal can be calculated as:

$$e=1\cdot d-a=e_{(-1)}+e_{(0)}+e_{(1)}+e_{(2)}+e_{(3)}$$

The resolution can easily be increased, but the monotonicity will soon be lost. In other words, the DNL as well as the INL is poor.

Distortion

For unit-element and scaled-element D/A converters, it is  $_{35}$  easy to show that the error signal e depends only on the instantaneous value of the input d, not upon previous inputs. The error signal e can, therefore, be described as harmonic distortion and intermodulation of d.

To help understand the ensuing theoretical explanations,  $_{40}$  it is important to understand the following:

- 1. The distortion of unit-element and scaled-element D/A converters will depend on the absolute error of each element in the D/A converter relative to the sum of all the elements. The distortion of a D/A converter will, 45 therefore, mainly depend on the relative error of its largest elements. The distortion of a D/A converter will in general not depend on its resolution (the number of levels which it can generate).

- When evaluating a D/A converter's distortion, a linear 50 trend may be removed from its input-output relation.

Two-level D/A converters will therefore be inherently linear (the only exception to the just mentioned rule concerning resolution).

Harmonic distortion and intermodulation are error types 55 to which many high-performance systems are sensitive. If a unit-element or scaled-element D/A converter is implemented in a mainstream CMOS or BiCMOS technology, the technology's matching properties will typically cause the THD to be in the order of -60 dB. That is not sufficient for 60 high resolution purposes.

Delta-Sigma D/A Converters

Delta-sigma D/A converters offer an inherently monotonic conversion which, without relying on matching, is essentially free of harmonic distortion and intermodulation. 65 Conceptually they are very different from the D/A converters discussed above.

4

Delta-sigma D/A converters are sampled systems. They do not convert each input sample separately. They convert the input signal as a whole and are therefore best described in the frequency domain; this technique which is a well-known to those skilled in the art. The Z-transformation will be denoted by  $Z\{\}$  and the Fast-Fourier-Transformation (FFT) will be denoted by  $F\{\}$ . As is common practice, a sampled signal, say x(k), may, without loss of information, be referred to by either its time-domain expression x(k) or its Z-transformed X(z). Notice that upper-case letters denote signals represented in the frequency domain, while lower-case letters denote signals represented in the time domain. The argument, z or k, will also indicate in which domain a signal is represented. Filters will be referred to by their transfer function H(z).

Basic Properties for Delta-Sigma D/A Converters

Delta-sigma D/A conversion is a tradeoff between resolution and speed. The frequency band of interest (which from now on will be called the signal band) of the input signal can only be a small fraction of the theoretically maximum bandwidth given by the Nyquist Theorem. The ratio of the Nyquist bandwidth  $f_N$  (half the sampling frequency) and the bandwidth  $f_B$  of the signal band is called the converter's over-sampling ratio (OSR):

$$OSR = \frac{f_N}{f_B} \gg 1$$

The operation of a delta-sigma D/A converter can be described as the combination of a nearly-ideal D/A converter followed by a low-pass filter with a narrow pass band.

As for any other D/A converter, the analog output signal a(k) will include an unwanted error signal e(k). An advantage of delta-sigma D/A converters is that e(k), besides being small, typically has properties similar to those of a noise signal; e(k) is not harmonic distortion nor intermodulation of d(k).

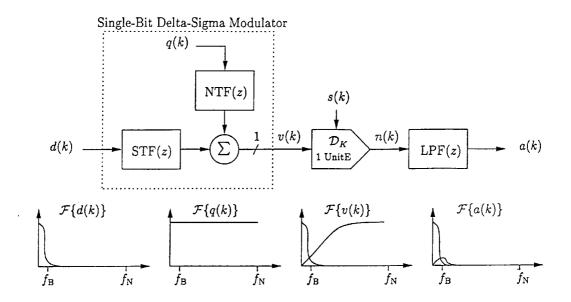

FIG. 4 shows a model of the operation of a traditional single-bit delta-sigma D/A converter. A digital delta-sigma modulator changes the high-resolution digital input d(k) into a single-bit digital signal v(k). Because v(k) is a single-bit signal, it can be D/A converted without introducing nonlinearities. The analog output a(k) is obtained by filtering of the output n(k) from the single-bit D/A converter.

Theory of Operation

The key in the system is the delta-sigma modulator. It is not obvious that it is possible to generate a single-bit signal v(k), such that a good estimate of d(k) can be obtained simply by filtering v(k). However, theory developed during the last few decades and numerous successful implementations have proved that it is indeed possible. An up-to-date description of how this can be done may be found in the book, *Delta-Sigma Data Converters; Theory, Design, and Simulation*, edited by Steven R. Norsworthy, Richard Schreier, and Gabor C. Temes, published by IEEE Press, 1996. Further references to this book will be by its title only.

Based on FIG. 4, the following discussion will provide insight into some fundamental properties of a delta-sigma D/A converter. Note that FIG. 4 does not attempt to illustrate how the modulator can be implemented; it merely models its signal conditioning operation.

Assuming that the two possible values of v(k) are  $\pm 1$ , the power of v(k) will be time-independent and equal to 1. Consequently, v(k) cannot track d(k) in power. Parseval's Theorem states that a signal's power is proportional to the integral of the square of the absolute value of its spectral components in the Nyquist band (from 0 to  $f_N$ ). The delta-

sigma modulator's job is to make the difference between v(k) and d(k) as small as possible in the signal band. Their difference in power will therefore have to be expressed as a difference in their spectral components outside the signal band (from  $f_B$  to  $f_N$  in FIG. 4). The qualitative properties of the spectral components of d(k), q(k), v(k), and a(k) are shown at the bottom of FIG. 4.

The internally generated signal q(k) is often called the "quantization noise." It is a deterministic signal, the sole cause of which is the low resolution of v(k). The modulator is designed such that the spectrum of q(k) has properties somewhat comparable to those of a white-noise signal. The modulator is said to be stable if q(k) remains bounded.

The transfer function NTF(z), by which q(k) is filtered before it is added to the signal path, is an inseparable part of the modulator. For well-designed modulators, NTF(z) will efficiently suppress the quantization noise in the signal band. The analog filter LPF(z) is intended to reject spectral components which are not in the signal band. All spectral components of q(k) will therefore be rejected by either NTF(z) or LPF(z). Leakage in the filter combination NTF (z)LPF(z) will degrade the converter's performance; the overall converter's error signal e(k) will be  $D_K(q(k))$  filtered by NTF(z)LPF(z), plus s(k) filtered by LPF(z) (the latter part is just an offset).

The ideal output of a delta-sigma D/A converter is  $D_K(d(k))$  filtered by the filter combination STF(z)LPF(z). Typically STF(z)LPF(z) will cause very little loss in the signal band.

Improving the Performance by Increasing the Order

The obtainable resolution of a delta-sigma D/A converter is determined by the power of q(k) and by the leakage in NTF(z)LPF(z).

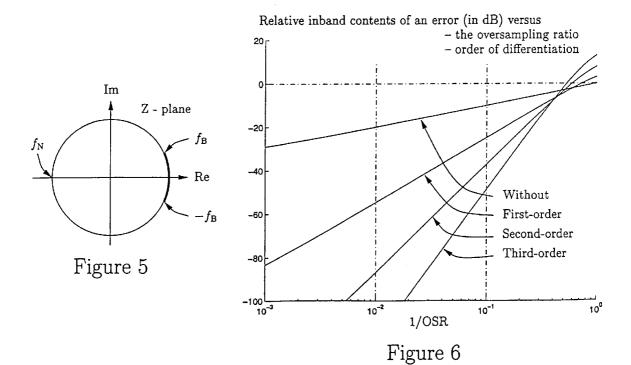

To minimize the leakage of NTF(z)LPF(z) in the signal band, NTF(z) must have one or more zeros located close to all segments of the Z-plane unit circle which corresponds to the signal band; this part of the Z-plane is marked with a heavy arc in FIG. 5. There are essentially two ways to obtain this:

- 1. Make the base band narrow (high OSR) and place one 40 or more zeros in the middle (z=1+0j).

- 2. If more than one zero is available, the leakage can be lowered by distributing the zeros in the base band. The leakage will still depend on the OSR; the higher the oversampling, the lower the leakage can be made.

The first solution is very simple, but it is typically not a good approach. The combination of the used technology and the system's power consumption limits  $f_N$ . Consequently, only applications with a narrow signal band can operate at a high OSR

# High-Order Modulators

If high resolution is required at a low OSR, the single-bit delta-sigma D/A modulator must be of high order (i.e. NTF(z) must have multiple zeros in the signal band). High-order single-bit delta-sigma modulators are, however, difficult to stabilize. Instability means that the magnitude of q(k) increases drastically, causing algorithmic overflow in the circuits, or otherwise poor system performance. Instability must be avoided, but the problem still is not fully solved. A design procedure is typically based on the trial-and-error principle. One rule of thumb, which gives a good starting point in the search for a good modulator, is to design NTF(z) as an Chebyshev-Passband high-pass filter with a peak gain of 1.6 or less.

# The Output Filter

To obtain a good overall performance, q(k) must also be efficiently suppressed in the rest of the frequency spectrum.

It is undesirable to design LPF(z) with a pass band which is significantly narrower than the stop band of NTF(z). In an optimum design, LPF(z) will have to be of at least the same order as the modulator. Since LPF(z) is an analog filter, it will unavoidably introduce errors, such as distortion, slewrate effects, etc. Since the power of the signal n(k) at the input of the filter LPF(z) is constant, such errors will not scale with the signal level of the input d(k) as they would in a more traditional analog system. The circuit-level difficulties associated with the design of LPF(z) often constitute the bottleneck in high-order single-bit delta-sigma D/A converters.

Improving the Performance Using Internal Multibit Quantization

By reducing the power of q(k), a delta-sigma D/A converter's performance will obviously be improved. For well-designed systems, the only way to significantly reduce the power of q(k) is to increase the resolution of v(k). Such systems are called "multibit delta-sigma D/A converters." They have a number of advantages compared to their single-bit counterparts:

- 1. The power of q(k) is reduced. This implies that the OSR or the order of NTF(z) and LPF(z) can be reduced.

- 2. The modulator is significantly easier to stabilize; NTF (z) can be chosen more freely.

- LPF(z) is easier to design because there is less noise to process.

These substantial advantages are quite obvious. Even so, systems have not been designed in this way until recently. 30 The problem has centered around the D/A conversion of the multi-level signal v(k). For example, if a unit-element D/A converter is used for this purpose, s(k) will include harmonic distortion of v(k) and thereby harmonic distortion of d(k). Derivations show that the THD of a multibit delta-sigma 35 D/A converter will be comparable to the THD of the D/A converter used internally in the signal path. The THD of a multibit system will therefore be in the order of -60 dB, unless excellent matching can be assured by calibration or other methods. Because any time-invariant two-level D/A converter is inherently linear, single-bit delta-sigma D/A conversion is a way to overcome the THD problem. Unfortunately, single-bit operation implies that a lot of shaped quantization noise will be included in the bit stream v(k).

45 Low-Resolution High-Linearity D/A Converters (LRHL-DACs)

Because multibit operation offers substantial system-level advantages, efforts have been made to design low-resolution high-linearity D/A converters (LRHL-DACs). In fact, increasing the resolution of v(k) from 2 to just 3 levels will have substantial advantages which can justify the implementation of a fairly complex internal D/A converter. Higher internal resolution will facilitate more system-level flexibility and improved performance, and hence more complex implementations of the internal D/A converter can be tolerated. U.S. Pat. Nos. 3,982,172; 4,125,803; 4,703,310; 4,791, 406; 5,134,402; and 5,534,863 describe techniques to implement LRHL-DACs which may be used for this purpose. However useful, such techniques may not be the best ones to use.

# Dynamic-Element-Matching D/A Converters

60

Instead of calibrating a low-resolution D/A converter to achieve high linearity (LRHL-DAC), it seems more promising to overcome element mismatch errors using dynamic element matching (DEM).

L. Richard Carley published a paper in the IEEE Journal of Solid-State Circuits, vol. 24, no.2, April 1989, describing

a three-bit D/A converter, for use in sampled systems, for which the error signal s(k) is uncorrelated with its input signal v(k). It is a unit-element D/A converter which, as usual, sums as many elements as the input prescribes. However, which elements are used in the sum is randomly chosen for each input sample.

By doing so, the converter becomes perfectly linear. The D/A converter's gain factor is the average value of the elements, and s(k) will be a white-noise signal. The Nyquistband power of s(k) is inversely proportional to the technolo- 10 gy's matching properties. In a typical technology, the power of s(k) will be in the order of 60 dB below full scale. However, because the filter LPF(z) removes most of this noise before it reaches the output, the noise contents in a(k) is inversely proportional to the OSR. In FIG. 6, the upper 15 curve, marked "Without," shows how much the noise will be suppressed as a function of the OSR. To achieve a signalto-noise ratio (SNR) of 90 dB, the system must operate at an OSR in the order of 1000; this is a system constraint which is highly impractical. Nevertheless, the unit-element D/A 20 converter using DEM is a historically important first example of a mismatch-shaping D/A converter.

As it was the case for delta-sigma D/A converters, a more efficient noise-shaping is required to make the concept commercially useful. As illustrated in FIG. 6, first- or 25 second-order mismatch-shaping will be sufficient for nearly all purposes.

The following section describes low-resolution mismatch-shaping D/A converters which are suitable for use in multibit delta-sigma D/A converters.

Mismatch-Shaping D/A Converters

The gain of a unit-element D/A converter using DEM is the average value of the unit elements. A problem with DEM is that this effect can only be observed using long estimates based on a large number of samples—an effect which is 35 directly related to the requirement of high over-sampling. Individual Level Averaging

A solution on the next level of sophistication was described by Bosco H. Leung and Sehat Sutarja in IEEE's *Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, Vol. 39, No. 1, January 1992. They describe a mismatch-shaping algorithm which they call for Individual Level Averaging (ILA).

The ILA algorithm can be described using a 4-level unit element D/A converter as an example. Level **0** can only be 45 generated by turning all 3 unit elements off. Level 1 can be generated in three ways—by separately turning on any one of the three elements. Level 2 can also be generated in three ways-by separately turning off any one of the three elements. Level 3 can only be generated by turning on all three 50 elements. Consequently, the D/A converter must be in one of 8 states: 1 state for the input code being 0, 3 states for the input code being 1, 3 states for the input code being 2, and I state for the input code being 3. For each input code, the ILA algorithm keeps track of which combinations have been 55 used in the past, and it always uses one of the combinations which so far has been used the least. Notice that the averaging is performed for each input code, therefore the name "Individual Level Averaging."

The advantage of the ILA algorithm, compared to the 60 DEM algorithm, is that the averaging is perfect whenever all combinations have been used the same number of times. Assuming that this occurs frequently, even short-term estimates of the error signal will have a fairly small standard deviation from the value zero. The result is that the ILA 65 algorithm can be used at a lower OSR than the DEM algorithm. The effect is verified by the simulation results

8

presented in FIGS. 17 and 18 in the paper by Leung and Sutarja. These Figures clearly show that the D/A converter's error signal is shaped by a high-pass filter. Although useful, the ILA algorithm has some serious disadvantages:

The algorithm's complexity is high; the hardware requirement increases faster than proportionally with the number of unit elements.

If an input code is rarely used, the averaging, and thereby the error cancellation, will take more time and the requirement for over-sampling increases.

A successful implementation of the ILA algorithm (controlling 8 unit elements) was reported by Feng Chen and Bosco H. Leung in IEEE's *Journal of Solid-State Circuits*, Vol. 30, No. 4, April 1995.

Data Weighted Averaging

A family of algorithms, called Data Weighted Averaging (DWA), offers a more efficient mismatch shaping at a lower complexity. Examples are discussed by Michael J. Story in U.S. Pat. No. 5,138,317; by Baird and Fiez in the *Proceedings to IEEE's International Symposium on Circuits and Systems*, 1995, pp. 13–16; by Jackson in U.S. Pat. No. 5,221,926; and by Adams in U.S. Pat. No. 5,404,142.

The advantage of DWA algorithms, compared to the ILA algorithm, is that averaging occurs more frequently and they can therefore be used at lower over-sampling ratios. Also, DWA algorithms are typically significantly simpler to implement than the ILA algorithm. Mathematical analysis shows that the error signal from a DWA D/A converter is first-order shaped, i.e., a bounded error, which is filtered by  $(1-z^{-1})$ .

FIG. 6 shows how much mismatch errors will be suppressed in the signal band as a function of the OSR and the order of shaping. Notice that the power is relative to the relative matching performance of the technology in which the D/A converter is implemented (assumed to be -60 dB). Using a DWA algorithm, a 16-bit D/A converter, operated at about 30 times oversampling, can therefore be implemented in a mainstream technology without post-processing calibration.

The element rotation scheme (ERS) is an example of a DWA algorithm. The unit elements are thought distributed on an oriented circle (like the numbers on an analog clock), and used sequentially. Using the analog-clock analogy for a 12-unit-element D/A converter, the conversion of the sequence 9,5,5,6,... would cause the following elements to be turned on in the conversions (each row shows the elements used to convert one sample):

$$\begin{aligned} & \{a_{unii::1}, \ a_{unii::2}, \ a_{unii::3}, \ a_{unii::4}, \ a_{unii::5}, \ a_{unii::6}, \ a_{unii::7}, \ a_{unii::8}, \ a_{unii::9}\} \\ & \{a_{unii::10}, \ a_{unii::11}, \ a_{unii::12}, \ a_{unii::1}, \ a_{unii::2}\} \\ & \{a_{unii::3}, \ a_{unii::4}, \ a_{unii::5}, \ a_{unii::6}, \ a_{unii::7}\} \\ & \{a_{unii::8}, \ a_{unii::9}, \ a_{unii::10}, \ a_{unii::11}, \ a_{unii::12}, \ a_{unii::1}\} \text{etc.} \end{aligned}$$

By using ERS, it is assured that all the elements are used equally often; perfect averaging occurs every time a full cycle is completed. The algorithm is highly useful and its complexity is low enough for use in D/A converters with up to 5–6 bits of resolution.

Higher-Order Mismatch Shaping

If speed is of great concern, high-order mismatch shaping may be desired to minimize the OSR, thereby increasing the converter's bandwidth. For example, by increasing the mismatch shaping from first to second order, the OSR for a typical 16-bit converter can be reduced by a factor of approximately 3 (from 30 to 10); such an improvement is highly desirable.

It is possible to obtain at least second-order shaping of mismatch errors. The known algorithms are, however, quite complex to implement; each unit-element will typically require a delta-sigma modulator of its own. Papers that describe such algorithms include the following: "Noise- 5 shaped multibit D/A converter employing unit elements" by R. Schreier and B. Zhang, published in Electronics Letters, Vol. 31, No. 20, 28th Sep., 1995; "Noise-Shaping D/A Converters for Delta-Sigma Modulation" by Ian Galton, published in Vol. 1 of Proceedings to IEEE's International 10 Symposium on Circuits and Systems, 1996; "Noise Shaping Dynamic Element Matching Method Using Tree Structure" by A. Yasuda and H. Tanimoto, published in Electronics Letters, Vol. 33, No. 2, 16th Jan., 1997.

The Resolution of Mismatch-Shaping D/A Converters

Mismatch shaping is an effective way to improve a D/A converter's performance for narrow-band applications. However, by only addressing unit elements, the resolution will remain somewhat limited.

Resolution is the main problem; a unit-element mismatch- 20 shaping D/A converter must be used in conjunction with a delta-sigma modulator and an analog filter LPF(z) to implement a high-resolution D/A converter. The hardware requirement to implement the known DWA algorithms is at least proportional to the number of unit elements. In other 25 words, the algorithms' complexities are at least exponentially related to the resolution measured in number of bits. Fortunately, most algorithms are fairly simple to implement when the resolution is low.

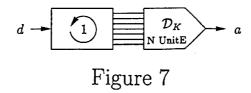

The Symbol

FIG. 7 shows the symbol which will be used to represent a mismatch-shaping coder driving a N unit-element D/A converter—in combination, a mismatch-shaping D/A converter. The number in the oriented circle shows the order of mismatch shaping the coder performs.

Dual-Quantization Delta-Sigma Converters

An alternative approach is described by Gabor C. Temes and Shao-Feng Shu in U.S. Pat. No. 5,369,403. It preserves the single-bit characteristic of v(k) and thereby eliminates s(k) as a problem to be concerned about. The consequences 40 of this design choice are well-known:

Large amounts of shaped quantization noise will be included in v(k).

The modulator, if it is of high order, will have to be stabilized by nonlinearities, such as saturation (also called hard-limiting or clipping) or reset of internal filter stages.

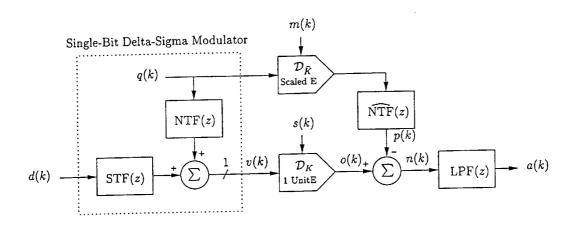

The Innovation

The dual-quantization topology is shown in FIG. 8. By introducing a noise-canceling path, the system compensates for the shaped quantization noise before it reaches the analog filter LPF(z). The main advantage is that the analog filter LPF(z) can be very simply implemented.

The Theory

By simple inspection, the following expression of the 55 signal o(k) can be derived:

O(z)=K [D(z)STF(z)+Q(z)NTF(z)]+S(z)

As shown in FIG. 8, a compensation signal

$P(z)=\hat{K}\cdot Q(z)NTF(z)$  is subtracted to eliminate the shaped quantization noise K·Q(z)NTF(z). The success of this scheme is based on the following assumptions:

That the quantization noise q(k) can be extracted from the

10

This can be obtained, for example by implementing the modulator as described in U.S. Pat. No. 5,369,403.

That q(k) can be filtered and D/A converted without introducing new errors.

Any multibit D/A conversion will be associated with the injection of an error signal. However, if q(k) is D/A converted before it is filtered by NTF(z), the error m(k), from the internal multibit D/A converter, will be efficiently suppressed in the system's signal band.

That the gains K and  $\hat{K}$  of the two D/A converters match. Analysis shows that this matching is not critical. If K matches K with a relative accuracy of, say, -50 dB, the shaped quantization noise will be reduced by 50 dB in the entire frequency spectrum. That is a major improvement.

That the analog replica NTF(z) matches the modulator's noise transfer function NTF(z).

This is the problem. It has proven very difficult to fulfill this requirement to the required extent. This will be discussed below.

Matching of First-Order Filters

It is known that a nearly ideal matching of NTF(z) and its

analog replica NTF(z) can be obtained if the delta-sigma modulator is of first order:  $NTF(z)=(1-z^{-1})$ . This is illustrated in FIG. 4 in U.S. Pat. No. 5,369,403. It is also described in section 10.4 in the book, Delta-Sigma Data Converters, Theory, Design, and Simulation. The problem is, however, that first-order modulators are so tonal that, even with a 50 dB reduction of the quantization noise, a high oversampling ratio will be required to obtain high performance.

Some improvement can be obtained by splitting the

transfer function NTF(z) between a stage applied before the D/A conversion and a single differentiation after the D/A converter (shown in FIG. 3 in U.S. Pat. No. 5,369,403). This

would preserve the matching of NTF(z) and NTF(z) while improving the signal-band performance. This will require some additional hardware. Furthermore, as it will be explained, if the OSR is to be low, then it may not work very we11.

45 Matching of Second-Order Filters

To obtain high performance at a low oversampling ratio, it is necessary to filter the output from the multibit D/A converter with a second- or higher-order analog filter. Such a filter will unavoidably cause significant nonidealities in the

The problem is not the suppression of the nonlinearity error signal m(k); it will be sufficiently suppressed unless the implementation of the filter is extremely poor. The problem is the difference in the phase shifts of the noise transfer

function NTF(z) and its part-analog replica NTF(z). Analysis shows that the compensation of the shaped quantization noise works well outside the signal band, but not in the signal band.

What is not generally known is that the above-mentioned problem can be solved. If the signal band quantization noise cannot be removed by compensation, the system should be designed not to rely on this. A way to obtain the insensitivity needed is to reduce the signal-band quantization noise in v(k), i.e., to increase the order of the modulator. By doing so, the system's signal-band performance may be degraded by about 3 dB (relative to plain single-bit operation); but the

out-of-the-signal-band quantization noise will be reduced significantly, say 50 dB. There are, however, a number of disadvantages:

To preserve good matching of  $\widehat{NTF}(z)$  and NTF(z), most 5

of NTF(z) should be implemented in the digital domain. This has hardware penalties.

A delta-sigma modulator of order higher than 2 will in general have to be stabilized by introducing nonlineari- 10 ties other than the quantizer. Examples of such nonlinearities include saturation and reset operations of the internal filter stages. When such operations are

performed, NTF(z) will not match NTF(z) and large 15 noise spikes will be encountered in n(k).

The main advantage of high-order dual-quantization delta-sigma D/A converters is that LPF(z) can be a simple low-order filter. However, if the filter must be able to remove such spikes, it is not easy to design. 20

## **OBJECTS AND ADVANTAGES**

Accordingly, several objects and advantages of this invention are listed below:

To provide a simple high-resolution oversampled D/A <sup>25</sup> second embodiment. converter which error signal has very little out-of-thesignal-band power. The analog filter LPF(z) can thereby be implemented as a very simple filter.

To provide a simple high-resolution oversampled D/A converter where the analog filter LPF(z) can be omitted. This requires that the system which the D/A converter is driving (for instance a set of headphones+ the human ear) provides some filtering.

To provide a high-resolution low-complexity scaled- 35 element mismatch-shaping D/A converter.

To provide a mismatch-shaping D/A converter with a complexity which is proportional to the resolution measured in bits.

To provide a second- or higher-order scaled-element 40 mismatch-shaping D/A converter.

To provide a conceptually new way to think of D/A conversion and to implement D/A converters.

To provide a D/A converter which is based on error compensation (like dual quantization) and which can be made of high order without being sensitive to modulator non-linearities;

does not generate spikes in the output; and does not rely on analog filters of order higher than one.

To provide a D/A converter which, without calibration and in a main-stream technology, will offer 16 bits of accuracy at around 10 times oversampling.

To provide a simple high-resolution mismatch-shaping D/A converter which does not delay the signal. It can, 55 therefore, be used as a feedback element in many types of A/D converters.

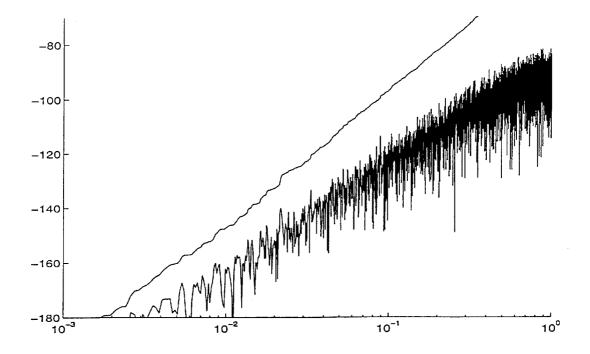

The list goes on; FIGS. 18 and 19 will adequately illustrate the superior performance which can be

Further objects and advantages will become apparent from a consideration of the drawings and ensuing descrip-

## DRAWING FIGURES

FIG. 1 shows the symbol which will be used to represent a generic (non-specified) D/A converter.

12

FIG. 2 shows the symbol which will be used to represent a unit-element D/A converter.

FIG. 3 shows the general concept for a binary-weighted D/A converter.

FIG. 4 shows a model which is used to explain the basic concept of delta-sigma D/A converters.

FIG. 5 shows, for a baseband delta-sigma D/A converter, where in the Z-plane the noise transfer function's zeros should be located.

FIG. 6 shows how much suppression of signal-band errors that mismatch shaping and oversampling can provide.

FIG. 7 shows the symbol which will be used to represent a unit-element mismatch-shaping D/A converter.

FIG. 8 shows the general concept for dual-quantization D/A converters.

FIG. 9 shows the general concept of D/A converters implemented according to this invention.

FIG. 10 shows a simple first embodiment of a D/A converter according to the invention.

FIG. 11 shows how a basic separator, as used in the first and other embodiments, can be implemented.

FIG. 12 shows how the separator is implemented in the

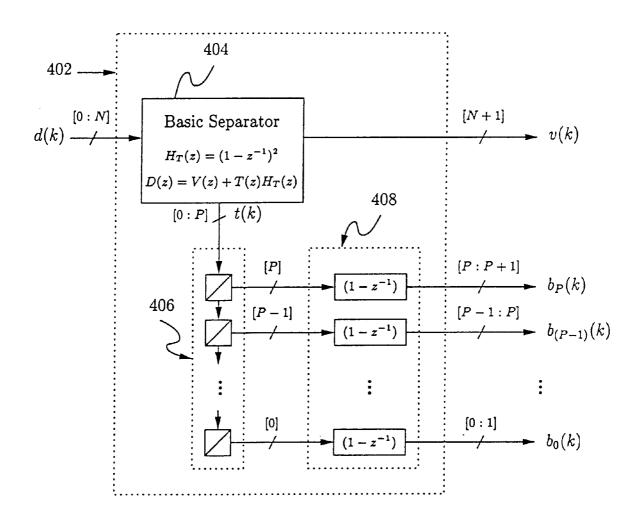

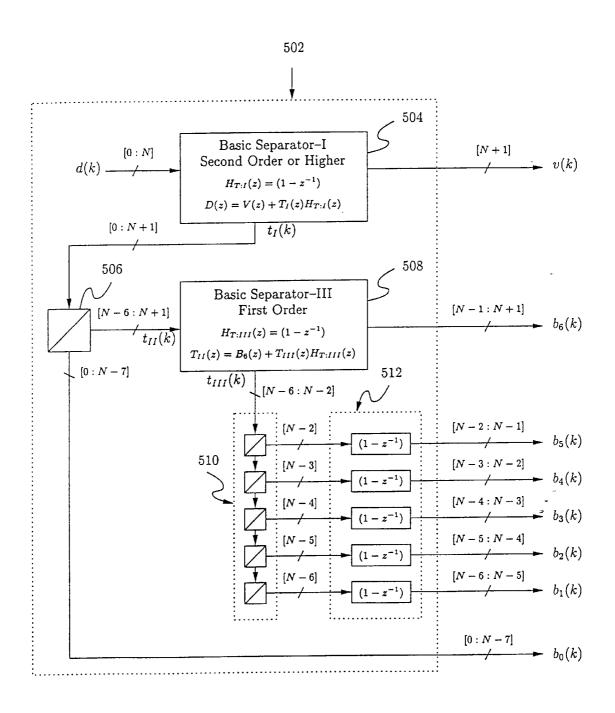

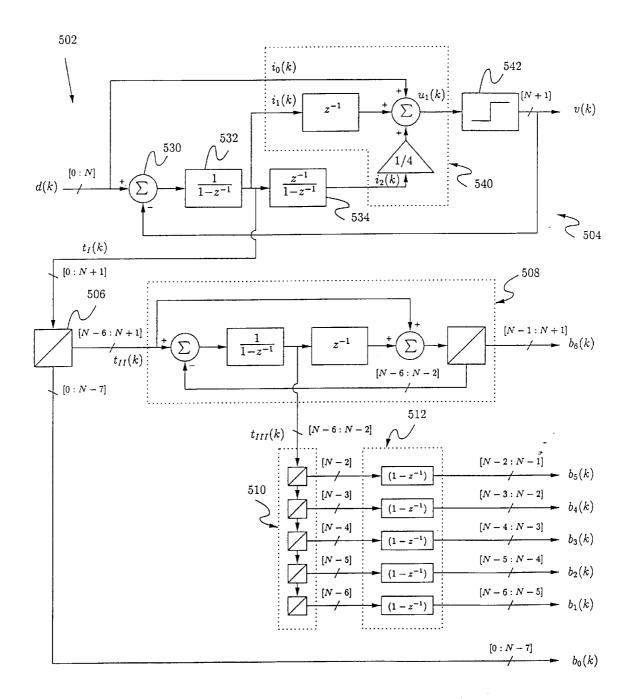

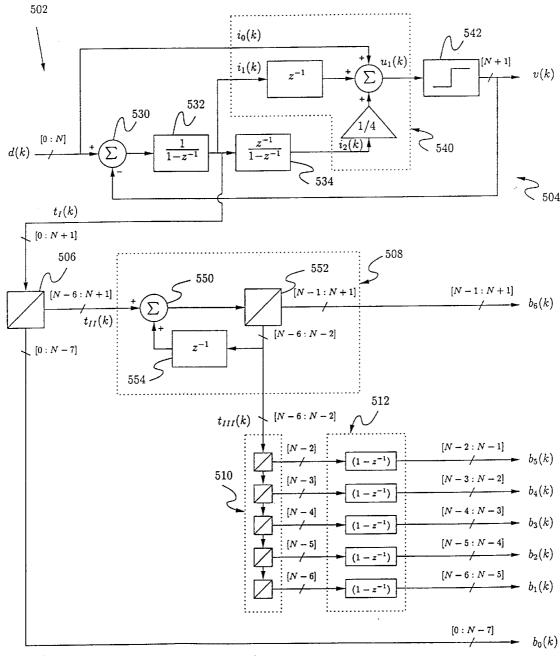

FIG. 13 shows how the separator is implemented in the third embodiment.

FIG. 14 shows how the separator is implemented in the fourth embodiment.

FIG. 15 shows in detail how the separator in the fourth embodiment can be implemented.

FIG. 16 shows in detail how the separator in the fourth embodiment can be implemented even simpler.

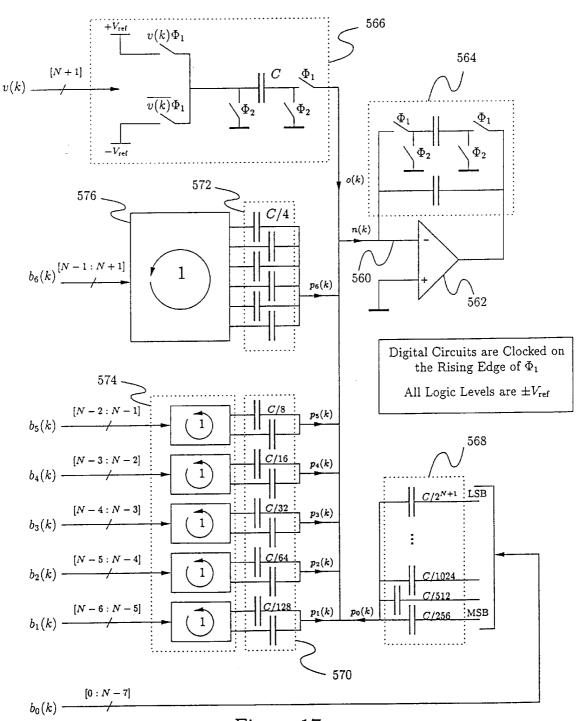

FIG. 17 shows in detail how the internal D/A converters and analog switch-capacitor filters, used in the fourth embodiment, can be implemented.

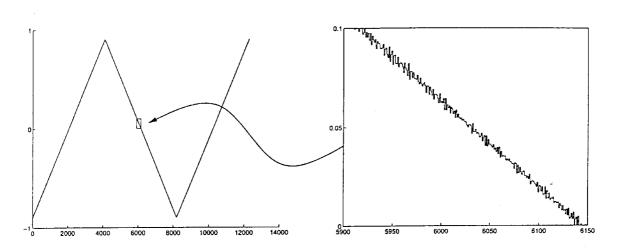

FIG. 18 shows the output waveform from the fourth embodiment when a sawtooth is applied as the input signal.

FIG. 19 shows the power-density spectrum (Fast-Fourier Transform) of the error signal in the fourth embodiment (data comes from the same simulation as in FIG. 18).

FIG. 20 shows how the fifth embodiment is implemented.

## REFERENCE NUMERALS IN DRAWINGS

100 General D/A converter system.

104 Main D/A converter.

108 Array of D/A converters

112 Analog adder. 116 Internal D/A converter.

120 Internal D/A converter.

124 Internal analog filter. 200 D/A converter system.

204 Main D/A converter (binary).

210 Analog filter (SC)

214 Analog signal-band filter. 230 Digital subtractor.

234 Second filter stage.

238 Fourth filter stage.

242 Quantizer.

302 Separator (main).

332 First filter stage.

336 First simple sub-separator.

340 Trailing filter section. 402 Separator (main).

406 Cascade of simple separators.

502 Separator (main).

506 Second sub-separator (simple).

102 General separator.

106 Main analog filter.

110 Array of analog filters.

114 Analog signal-band filter. 118 Internal D/A converter.

122 Internal analog filter.

126 Internal analog filter. 202 Separator (main).

208 D/A converter.

212 Analog adder.

232 First filter stage.

236 Third filter stage.

240 Controller.

330 Digital subtractor.

334 Second filter stage

338 Second simple sub-separator.

342 Controller.

404 First sub-separator (basic).

408 Array of digital filters.

504 First sub-separator (basic).

508 Third sub-separator (basic).

## -continued

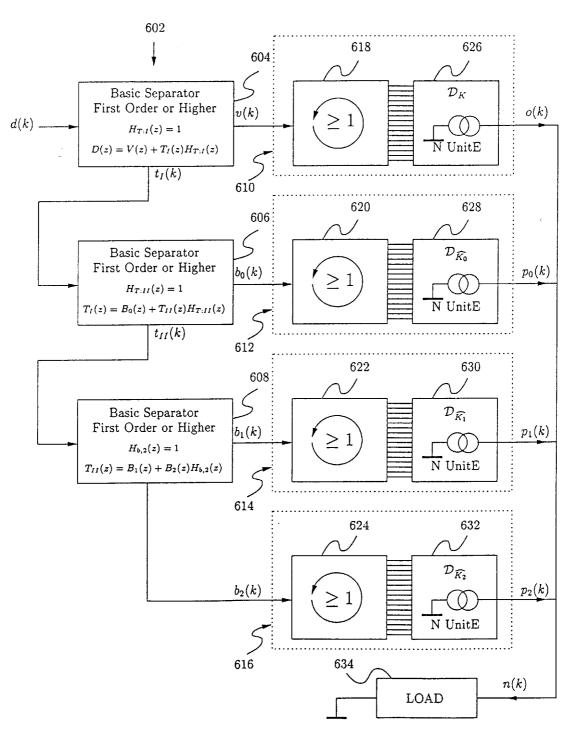

512 Array of digital filters. 510 Fourth sub-separator. 530 Digital subtractor. 532 First filter stage 534 Second filter stage 540 Controller. 550 Digital adder. 542 Quantizer. 552 Simple separator (quantizer). 554 Delay element. 560 Common node. 562 Operational amplifier. 564 Feedback element. 566 Main D/A converter (binary). 568 Binary weighted capacitors. 570 Array of capacitor pairs. 572 Array of identical capacitors. 574 Array of DWA coders. 576 DWA coder. 604 First sub-separator (basic). 602 Separator (main). 606 Second sub-separator (basic). 608 Third sub-separator (basic). 610 Main mismatch-shaping DAC. 612 Mismatch-shaping DAC. 614 Mismatch-shaping DAC. 616 Mismatch-shaping DAC. 618 DWA coder. 620 DWA coder. 622 DWA coder. 624 DWA coder. 626 Unit-element current DAC. 628 Unit-element current DAC. 630 Unit-element current DAC 632 Unit-element current DAC 634 Load.

## SUMMARY OF THE INVENTION

According to this invention, a D/A conversion includes the following steps: separation into a plurality of signals, individual D/A conversion of the plurality of signals (possibly by mismatch-shaping D/A converters), individual filtering of the plurality of signals, summing of the plurality of D/A-converted and filtered signals, and if necessary a final analog filtering.

# DESCRIPTION OF PREFERRED **EMBODIMENTS**

To begin with, the general structure is described. This is done to give the reader a general understanding of the nature of the disclosed D/A converter systems. Guidelines are given for how to design and optimize a system. Then, five preferred embodiments will be described. The embodiments are increasingly more sophisticated attempts to meet the design guidelines.

The first embodiment illustrates a simple system which is somewhat similar to a dual-quantization D/A converter. There are, however, important differences and advantages. The basic separator, which is a key element, is described in

The second embodiment shows a generalization of the  $_{45}$ basic separator. The purpose of this embodiment is to give the designer an extra tool to design a separator to meet specific needs.

The third and fourth embodiments illustrate how a second-order scaled-element mismatch-shaping D/A converter system based on switched-capacitors circuits can be implemented in a basic integrated circuit technology. These embodiments are found to be highly useful for integrated circuit applications.

The fifth embodiment illustrates how it is possible to 55 make use of the invention in systems where there are few design options (for instance in high-power systems). Definitions and Terminology

This section will define the terms, "bit number" and "separator." These terms will be used repeatedly in the 60 description of the invention.

Definition of the Term, "Separator"

A separator is a system that separates an input d(k) into a main signal v(k) and one or more compensation signals  $b_0(k), b_1(k), \ldots, b_N(k)$ . The only requirement is that there 65 2. Similarly, the transfer functions  $\widehat{H}_{B_0}(z), \widehat{H}_{B_1}(z), \ldots$ exists a set of filters  $H_D(z)$ ,  $H_V(z)$ ,  $H_{B:0}(z)$ ,  $H_{B:1}(z)$ , ...,  $H_{B:N}(z)$ (z) for which the following Equation 1 is fulfilled:

14

$$D(z)H_D(z)=V(z)H_V(z)+B_0(z)H_{B:0}(z)+B_1(z)H_{B:1}(z)+\dots+B_N(z)H_{B:N}(z)$$

Note that Equation 1 does not completely describe a separator. Different separators may be described by the same Equation 1.

Terminology When Referring to a Bit in a Signal

Signals of various magnitude and resolution will be discussed repeatedly. To prevent confusion, a consistent 10 terminology will be introduced. The binary number system is used as an example, but it is to be understood that other number systems can be used as well.

All signals occurring in the discussed embodiments are represented in the binary number system. If negative numbers are to be represented, then a two's complement coding is appropriate. It is assumed that any digit occurring in any signal in the discussed embodiments will have a weight which is a power of two,  $1=2^{\circ}$  being the lowest weight used. The digit terminology will not be used. The signals will be represented by their bits; i.e., the digits combined with their weights. Any bit in any signal will therefore always represent one of two possible values: 0 or  $2^i$  where i is an integer or zero. The only exception is the most significant bit in a signal represented by a two's complement (where the possible values are 0 and  $-2^{i}$ ).

The text refers to a bit's number as the power of two in its non-zero value. For example, "the third bit" refers to the bit which can have only the two values 0 or ±8. A bit's number does not refer to its position relative to the least 30 significant bit in the signal. The terms, "least significant bit" (LSB) and "most significant bit" (MSB), do only make sense when they refer to a specific signal. The MSB of a signal is the bit (in that signal) which has the highest bit number. The LSB of a signal is the bit (in that signal) which has the lowest bit number. Therefore, the terms MSB and LSB do not refer to specific bit numbers.

Description of the General Structure

FIG. 9 shows the general structure [100] of an oversampled D/A converter system according to the invention. A separator [102] separates a digital input signal d(k) into a main digital signal v(k) and a set of one or more digital compensation signals:  $b_0(k), b_1(k), \dots, b_N(k)$ . The operation of the separator [102] can be described by Equation 2:

$$D(z)H_{D}(z) = V(z)H_{V}(z) + \sum_{i=0}^{N} B_{i}(z)H_{B:i}(z)$$

(2)

The main signal v(k) is D/A converted by a main D/A converter [104] and filtered by a main analog filter [106] whereby a main analog signal o(k) is generated. The compensation signals  $b_0(k)$ ,  $b_1(k)$ , . . . ,  $b_N(k)$  are individually D/A converted by an array of D/A converters [108] and subsequently filtered by an array of analog filters [110], whereby a set of analog compensation signals  $p_0(k), p_1(k), \dots, p_N(k)$  is generated.

The gain K of the main D/A converter [104] and the gains

$\widehat{K_0}$ ,  $\widehat{K_1}$ , ...,  $\widehat{K_n}$  of the other D/A converters [108] are designed to match the same value K. The transfer function

H<sub>x</sub>(z) of the main analog filter [106] should be designed to match  $H_{\nu}(z)$  of the separator [102], as described by Equation

$H_{RN}(z)$  of the filters in the array of analog filters [110]

should be designed to match the transfer functions  $H_{B:0}(z)$ ,  $H_{B:1}(z), \ldots, H_{B:N}(z)$  of the separator [102], as described by Equation 2.

The main analog signal o(k) and the analog compensation signals  $p_0(k)$ ,  $p_1(k)$ , ...,  $p_N(k)$  are added in an analog adder 5 [112]. The output from the adder [112], called the analog estimation signal n(k), is filtered by an analog filter [114] to form the overall analog output signal a(k).

FIG. 9 shows three D/A converters [118] [118] [120] in the array of D/A converters [108] and, consequently, three 10 filters [122] [124] [126] in the array of analog filters [110].

Is is to be understood that the general structure [100] and the invention as such include the following variations:

There can be a single compensation signal as well as a multitude of compensation signals.

Some or all the analog filters [106] [110] [114] may be simple signal paths.

Some of the analog compensation signals may not be generated or included in the analog estimation signal 20 will in the following be called "gain-mismatch errors." The

Operation of the General Structure

The main digital signal v(k) and the digital compensation signals  $b_0(k)$ ,  $b_1(k)$ , . . . ,  $b_N(k)$  are individually D/A converted and filtered to form the main analog signal o(k) 25 and the analog compensation signals  $p_0(k)$ ,  $p_1(k)$ , ...,  $p_N(k)$ . The scaling and filtering of the signals o(k),  $b_0(k)$ ,  $b_1(k)$ , . . .,  $b_N(k)$  are chosen according to Equation 2, such that the sum of the signals o(k),  $p_0(k)$ ,  $p_1(k)$ , ...,  $P_N(k)$ , the analog estimation signal n(k), in the ideal case is an analog replica 30 of the digital input signal d(k).

Modeling Errors

Due to circuit imperfections, errors will be injected in the system [100] and become a part of the analog estimation signal n(k). The purpose of the separation is to facilitate the 35 filtering, or suppression by other means, of the errors in the signal band before they are included in the estimation signal n(k).

The following discussion will assume that the analog signal-band filter [114] is a simple signal path (i.e., LPF(z)= $^{40}$ 1). The designer may choose to implement a simple filter [114], but, as it will be demonstrated, it will in many cases not be necessary.

As will be described, the main D/A converter [104] will nearly always define the system's [100] gain. Using this gain K as the reference, Equation 2 describing the separator [102], leads to Equation 3, which describes the analog estimation signal n(k) in the ideal case:

$$N_{ideal}(z) = K \left[ V(z) H_{V}(z) + \sum_{i=0}^{N} B_{i}(z) H_{B:i}(z) \right]$$

(3)

However, due to element mismatch, the analog estimation 55 signal will instead be described by

$$N_{actual}(z) = KV(z)\hat{H_V}(z) + S(z)\hat{H_V}(z) + \sum_{i=0}^{N} \left[ \hat{K_i}B_i(z) + M_i(z) \right] \hat{H_{B;i}}(z), \tag{4}$$

where a(k) is the error signal from the main D/A converter [104] and  $m_i(k)$  the error signals from the other D/A converters [108].

By subtracting Equation 3 from Equation 4, Equation 5 65 expressing the D/A converter system's [100] error signal is obtained:

16

$$E(z) = KV(z) [\hat{H}_{V}(z) - H_{V}(z)] +$$

$$\sum_{i=0}^{N} B_{i}(z) [\hat{K}_{i} \hat{H}_{B:i}(z) - K H_{B:i}(z)] +$$

$$S(z) \hat{H}_{V}(z) + \sum_{i=0}^{N} M_{i}(z) \hat{H}_{B:i}(z)$$

(5)

The first part of the error signal,  $KV(z)[\hat{H}_{v}(z)-H_{v}(z)]$ , is not critical; especially in the typical case where the main analog filter [106] is a simple signal path.

The second part of the error signal,

$$\sum_{i=0}^{N} B_{i}(z) \left[ \hat{K}_{i} \hat{H}_{B:i}(z) - K H_{B:i}(z) \right],$$

third part of the error signal,

$$S(z)\hat{H_V}(z) + \sum_{i=0}^{N} M_i(z)\hat{H_{B:i}}(z),$$

will be called "nonlinearity errors." These definitions will turn out to be very useful when the system [100] is to be designed and evaluated. Notice that this model is just one of many possible models.

Nonlinearity Errors

Nonlinearity errors are due to element mismatch within each D/A converter [104] [108]. In other words, it is a local mismatch that is defined with respect to the specific D/A converter of consideration.

Gain-Mismatch Errors

Gain-mismatch errors are, on the other hand, globally defined. They are caused by mismatch of the gains of the individual D/A converters in the array of D/A converters [108] relative to the gain of the main D/A converter [104].

The purpose of the separation performed by the separator [102] is to facilitate suppression of all errors in the signal band. Below is described how this can be obtained. Suppression of Gain-Mismatch Errors

All gain-mismatch errors are of the same structure which is the product of a compensation signal b<sub>i</sub>(k) and the

difference between two filters

$$[\widehat{K}_i \widehat{H}_{B:i}(z) - KH_{B:i}(z)]$$

.

Matching an analog filter's transfer function  $\widehat{K}_{+}\widehat{H}_{B:}(z)$  to the transfer function  $KH_{B:}(z)$ , which is defined by the digital separator [102], is a very difficult design task. It is generally unwise to let the operation of a converter depend heavily on such a matching. There is, however, an exception; if the filter is a first order difference,  $H_{B:i}(z)=(1-z^{-1})$ , then a switched-

capacitor implementation of  $\widehat{H_{\text{B};i}}(z)$ = $(1-z^{-1})$  can be expected to match very well. This will be exemplified in a preferred embodiment.

Those skilled in the art will be able to, when evaluating 60 a given circuit, evaluate the worst-case transfer function

$[K_1 H_{B_2}(z) - KH_{B_2}(z)]$ . This evaluation can be used to estimate the suppression of the compensation signal b<sub>i</sub>(k) as an

In the embodiments used as examples, matching the gain

factors  $[K_i-K]$  is the main concern. When the error signals

are referred to full-scale output, it is, however, the relative matching of the gain factors which is of interest. Conclusion

When  $\hat{H}_{B:i}(z)$  can be expected to accurately match  $H_{B:i}(z)$ , 5 the gain-mismatch errors can be modeled as the filtered compensation signals H<sub>B.</sub>(z)B<sub>1</sub>(z), suppressed by 50–60 dB (typical expected value for relative matching of gain factors when a mainstream technology is used).

Even if good matching of high-order filters cannot be 10 assured, a very low signal-band contents of gain-mismatch errors can be obtained by designing the separator [102] such that the digital compensation signals have very little power in the signal band (i.e., using shaped compensation signals). Obviously, a small compensation signal will have a small overall power; it will therefore not have to be shaped as much as a large compensation signal.

Comment on Dual-Quantization D/A Converters

The general structure [100] can also model dualquantization D/A converters. They have only one compen- 20 in many ways and to meet various needs. The following list sation signal, the quantization noise, and accordingly only

one gain-mismatch error:  $Q(z)[\hat{K} NTF(z)-K NTF(z)]$ . The reason why dual-quantization D/A converters are difficult to implement is that the compensation signal is not shaped (it 25 is usually modeled as white noise). Consequently, the success of the topology depends heavily on how well the filter

$\hat{K}$  NTF(z) matches K NTF(z). Suppression of Non-Linearity Errors

There are two kinds of nonlinearity errors: the main

nonlinearity error  $S(z)\hat{H}_{\nu}(z)$  from the main D/A converter [104] and the nonlinearity errors

$$\sum_{i=0}^{N} M_i(z) \hat{H_{B:i}}(z)$$

pensation signals.

To suppress gain-mismatch errors, one signal is required to carry the main part (the signal-band contents) of the input signal d(k). This is the purpose of the main digital signal

that H<sub>\(\infty\)</sub>(z) will not suppress the signal band significantly. Any signal-band part of the main nonlinearity error s(k) will, therefore, flow directly to the estimation signal n(k). Consequently, the main D/A converter [104] should be designed either as a two-level or as a mismatch-shaping D/A converter.

A second-order mismatch-shaping D/A converter will be demonstrated as a preferred embodiment. To avoid the complexity of implementing a second-order unit-element 55 mismatch-shaping D/A converter, the main D/A converter [104] can be chosen as a two-level device.

The other nonlinearity errors

$$\sum_{i=0}^{N} M_i(z) \hat{H_{B:i}}(z)$$

are caused by the D/A converters [108] converting the digital compensation signals. These errors will be filtered by 65 the analog filters [110] which can be designed to suppress the signal band.

18

Conclusion

The main nonlinearity error  $S(z)\hat{H}_{\nu}(z)$  can be avoided by choosing the main digital signal v(k) as a binary (two-level) signal. If v(k) is a multi-level signal, the main D/A converter [104] should be mismatch-shaping.

The other nonlinearity errors can be suppressed in two ways: either by using mismatch-shaping D/A converters [108] or by designing the separator [102] such that the analog filters [110] suppress the signal band. The two techniques can be combined; first-order mismatch-shaping D/A converters [108] followed by first-order analog filters [110] will result in second-order-shaped nonlinearity errors.

Obviously, if a compensation signal is small, then the 15 respective nonlinearity error will have a small overall power. It will, therefore, not require as much shaping as a nonlinearity error from large compensation signals. Design Strategy

It will be demonstrated that the separator can be designed summarizes what can and should be done to obtain good performance at low cost:

The main D/A converter [104] must be as good as the overall system specification [100]. It should be implemented as a two-level or mismatch-shaping D/A converter [104].

Large compensation signals can be shaped to help suppress gain-mismatch errors.

Nonlinearity errors can be shaped by analog filters [110]. Nonlinearity errors can be shaped by using mismatchshaping D/A converters [108].

Large compensation signals should have a low resolution (to keep the mismatch-shaping D/A converters [108] simple).

Small compensation signals will cause small errors. Hardware may be saved by shaping these signals less.

A First Embodiment

35

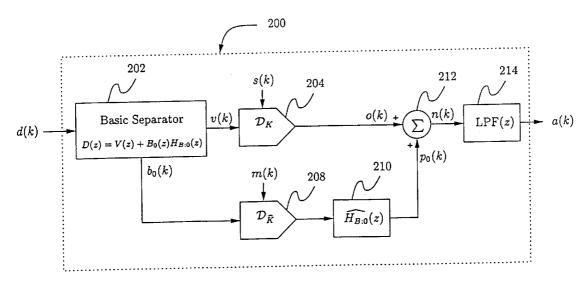

FIG. 10 shows a first embodiment of the general structure from the D/A converters [108] converting the digital com- 40 [100]. FIG. 10 and subsequent Figures illustrating other embodiments will use numerals different from those used in FIG. 9.

Description of the First Embodiment

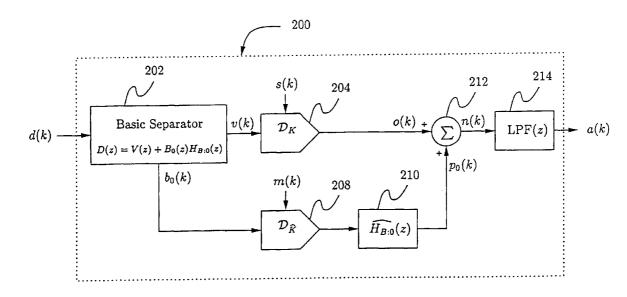

The separator [202] in FIG. 10 implements the separator v(k), thus it is nominated to be the main signal. This implies 45 [102] in the general structure [100]. It separates the digital input signal d(k) into the main digital signal v(k) and only one digital compensation signal  $b_0(k)$ . The main digital signal v(k) is converted by a main D/A converter [204] implementing the main D/A converter [104] in the general structure [100]. The main analog filter [106] is a simple signal path, so the output from the main D/A converter [204] is the main analog signal o(k). The digital compensation signal  $b_0(k)$  is D/A converted by a D/A converter [208], and subsequently filtered by an analog filter [210] providing the only analog compensation signal p<sub>0</sub>(k). The main analog signal o(k) and the analog compensation signal p<sub>0</sub>(k) are added in an analog adder [212] providing the analog estimation signal n(k). The analog estimation signal n(k) is optionally filtered by an analog filter [214], removing out-60 of-the-signal-band errors.

> Except for the separator [202], the system [200] is comparable to a dual-quantization D/A converter described in the prior art. In this embodiment, it is assumed that the two D/A converters [204] and [208], the analog filters [210] and [214], and the analog adder [212] are implemented according to the prior art. FIG. 4 in U.S. Pat. No. 5,369,403; FIGS. 10.18 and 10.33 in the book Delta-Sigma Data Converters;

Theory, Design, and Simulation, and the text accompanying those Figures, illustrate appropriate techniques for this purpose. The separator [202] is, however, implemented in a novel and improved way. It will be described in detail in a following section.

Operation of the First Embodiment

The general structure [100] and its operation was described in a previous section. The key component is the separator [202], which separates the input signal d(k) according to Equation 6:

$$D(z)=V(z)+B_0(z)H_{B:0}(z)$$

(6)

according to which the remaining part of the system [200] is to be designed.

In the generation of the main digital signal v(k), the 15 separator [202] operates as a delta-sigma modulator. However, by extracting additional signals from the modulator, it becomes a separator. It is a key point that the delta-sigma modulator can be designed without paying much attention to the transfer function  $H_{B:0}(Z)$ . Consequently, the separator [202] can be designed such that there, in the signal band, is very little difference between the input signal d(k) and the main output signal v(k). The difference between these two signals is described by  $B_0(z)$  $H_{R,0}(z)$ . Consequently, if the delta-sigma modulator is designed of a higher order than the order of the transfer function  $H_{B:0}(z)$ , the compensation signal  $b_0(k)$  will have relatively less power in the signal band (it is shaped). Gain-Mismatch Errors

According to the description of the general structure 30 [238]. [100], it is an advantage that the compensation signal  $b_0(k)$ is shaped. The advantage is that the signal-band contents of

the gain-mismatch error  $B_0(z)[\widehat{K_0}\widehat{H_{B:0}}-KH_{B:0}]$  will be less dependent on the cancellation in the second term 35

$[\hat{K}_0 \hat{H}_{B:0} - KH_{B:0}]$ . In other words, the system's [200] signalband performance will be less sensitive to whether the analog filter [210] has the exact transfer function  $H_{B:0}(z)$  or whether it is just a close match. A given performance can 40 therefore be obtained using less ideal circuitry. In reality, it is a requirement to make a high-performance system work at all.

Non-Linearity Errors

Assuming that the main D/A converter [204] is a two- 45 level or a mismatch-shaping D/A converter, the nonlinearity error s(k) will be small in the signal band.

Because the resolution of the compensation signal b<sub>0</sub>(k) is high, it will have to be D/A converted by a non-mismatchshaping D/A converter [208], for example a scaled-element 50 D/A converter. The nonlinearity error from this D/A converter [208] will be m(k) filtered by the analog filter [210]. Because the power of m(k) will be considerably, say by 60 dB, smaller than the power of the analog estimation signal the analog filter [210] can therefore be low.

An Example

Assume that the separator [202] is of second order while the analog filter [210] is of first order.

Basic technologies typically offer a relative matching of 60 around -60 dB for large geometries. In such a technology, the system will offer a performance which is described by a first-order-shaped error with a -60 dB Nyquist-band power. According to FIG. 6, that is equivalent to about 16 bits of accuracy at 30 times of oversampling.

The system can also be designed to offer second-order noise-shaping, but a more efficient topology will be discussed as another embodiment. The following will describe the separator [202] in detail.

Description of the Basic Separator

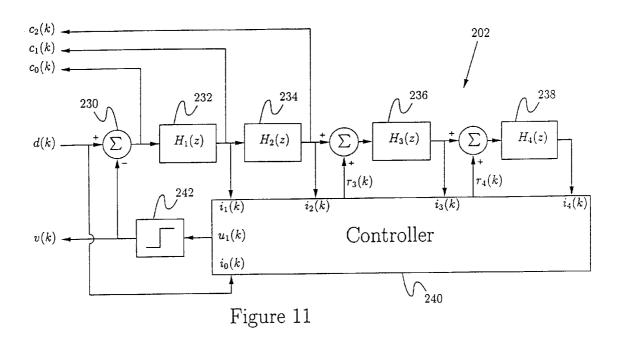

FIG. 11 shows how the separator [202] can be implemented by means of a delta-sigma modulator. This separator [202] is a fundamental building block which will be used again and again. It will be referred to as the "basic separator."

The basic separator [202] produces two output signals v(k) and  $b_0(k)$  as a function of the input signal d(k). The signals v(k) and d(k) are the same in FIGS. 10 and 11. The compensation signal  $b_0(k)$  in FIG. 10 can be one of the three signals  $c_0(k)$ ,  $c_1(k)$ ,  $c_2(k)$  shown in FIG. 11. The operation, but not the implementation, of the basic separator [202] will depend on which one of these three signals is used as the compensation signal b<sub>0</sub>(k). The choice determines the transfer function  $H_{B:0}(z)$  which characterizes the separator [202] as described by Equation 6.

The Structure

A digital subtractor [230] subtracts the main digital signal v(k) from the digital input signal d(k). The result from this subtraction is used as input to a first filter stage [232]. The output of the first filter stage [232] is used as input to a second filter stage [234]. The output of the second filter stage [234] is added to a signal r<sub>3</sub>(k), which is supplied by a controller [240], and the result is used as input to a third filter stage [236]. The output of the third filter stage [236] is added to a signal r<sub>4</sub>(k), which is also supplied by the controller [240], and the result is used as input to a fourth filter stage

The controller [240] generates three signals:  $u_1(k)$ ,  $r_3(k)$ , and  $r_4(k)$ . These three signals are generated as a function of five input signals: io(k) which is the same as the separator's [202] input signal d(k), and the output signals,  $i_1(k)$ ,  $i_2(k)$ ,  $i_3(k)$ , and  $i_4(k)$ , from the four filter stages [232] [234] [236] [238].

The signal u<sub>1</sub>(k), generated by the controller [240], is fed to a quantizer [242]. The output from the quantizer [242] is the separator's [202] main output v(k). The signal  $c_0(k)$  is the output from the digital subtractor [230]; the signal cl (k) is the output from the first filter stage [232]; and the signal c<sub>2</sub>(k) is the output from the second filter stage [234]. Variations

It is to be understood that the separator as well can be based on more of fewer filter stages. It is important to note that no signals, except d(k) and v(k), are fed to any node in the chain of filters [232] [234] [236] [238] which has a signal path to the compensation signal bo(k) that does not pass through the quantizer [242]. For example, if  $c_1(k)$  is used as the compensation signal  $b_0(k)$ , it is allowed to add a signal r<sub>2</sub>(k) from the controller [240] to the input of the second filter stage [234]. This is, however, not allowable if  $c_2(k)$  is used as the compensation signal b<sub>0</sub>(k). As exemplified by a second embodiment, this rule may be violated, but it n(k), it will not have to be shaped very much. The order of 55 requires careful consideration of how the digital input signal d(k) can be reconstructed on basis of the main digital signal v(k) and the compensation signals b<sub>i</sub>(k).

Operation of the Basic Separator

The basic separator [202], considered from the input d(k) to the main output v(k) will be recognized, by those skilled in the art, as a generic delta-sigma modulator implemented in a specific topology (often called the "Cascaded Integrators Feed-Forward," or CIFF topology). For instance, compare FIG. 11 with FIGS. 5.6 and 5.7 in the book, Delta-Sigma Data Converters; Theory, Design, and Simulation. One can identify that the controller [240] there generates  $u_1(k)$ ,  $r_3(k)$ ,  $r_4(k)$  as scaled sums of  $i_0(k)$ ,  $i_1(k)$ ,  $i_2(k)$ ,  $i_3(k)$ ,

and i<sub>4</sub>(k). Many delta-sigma modulators are designed in this way. The coefficients in these scaled sums can for instance be obtained using a design tool like The Delta-Sigma Toolbox written by Richard Schreier. At the time of this writing, this excellent toolbox was offered for free and can be found on the Internet (anonymous FTP) at: "next242.ece.orst.edu/pub/delsig.tar.Z." Analysis

The operation of the basic separator [202] is remarkably simple to analyze (assuming that the controller assures the 10 system's stability). According to the definition of subtraction, the operation of the subtractor [230] can be described as follows:

$$c_0(k) = d(k) - v(k)$$

i.e.  $D(z) = V(z) + C_0(z)$  (7)

According to the definition, the system is a separator when  $c_0(k)$  is used as the only compensation signal  $b_0(k)$ .

Another separation, which is more useful for the first embodiment, results if  $c_1(k)$  is used as the only compensa- 20 tion signal  $b_0(k)$ :

$$C_1(z) = H_1(z)[D(z) - V(z)]$$

i.e.  $D(z) = V(z) = \frac{C_1(z)}{H_1(z)}$  (8)

For the basic separator [202], and for delta-sigma modulators in general, the filter stages [232] [234] [236] [238] in the loop have high gain in the signal band. Consequently, the separation performed by is separator [202] will, as desired, cause the spectral components of  $c_1(k)$ , including any errors, to be suppressed in the signal band before they are included in the analog output signal.

For example, for a baseband modulator, the first filter stage can be an integrator;

$$H_1(z) = \frac{1}{1-z^{-1}}.$$

In that case, the following very useful separation will be 40 performed:

$$D(z)=V(z)+C_1(z)(1-z^{-1})$$

(9)

to implement the filter stages as delaying integrators;

$$H_1(z) = \frac{z^{-1}}{1 - z^{-1}}.$$

In that case, the following separation will be performed, assuming that  $c_1(k)=b_0(k)$ :

$$z^{-1}D(z) = z^{-1}V(z) + C_1(z)(1 - z^{-1})$$

(10)

This Equation expresses that v(k) and  $c_1(k)$  can be combined to form d(k) delayed by one sample. In some applications, such as compact-disc-playback units etc., delay is perfectly tolerable. For other applications, for instance when used as a feedback element in an A/D converter, delay may not be tolerable. Fortunately, it is always possible to redesign the controller [240], and replace a delaying filter stage [232] [234] [236] [238] by a non-delaying stage. Conclusion

No matter from which point in the chain of filter stages 65 [232] [234] [236] [238] the compensation signal  $b_0(k)$  is extracted, the separation can be written in the form:

$$D(z)=V(z)+C(z)H_{B:0}(z)$$

(11)

In this Equation,  $H_{B:0}(z)$  is the reciprocal of the product of the transfer functions of the filter stages [232][234] between the subtractor [230] and the node from which  $b_0(k)$  is extracted.

If one or more filter stages are delaying, Equation 11 may have to be multiplied by  $z^{-\omega}$ , corresponding to a delay of  $\omega$  samples, to make  $H_{B:0}(z)z^{-\omega}$  implementable.

Must the Controller be Linear?

The only assumptions made in the above analysis were that the filter stages [232] [234] used in the expression for  $H_{B:0}(z)$  have high gain in the signal band and that the (7) 15 modulator is stable. As explained below, the quantization noise is not a parameter to be concerned about.

> The quantization noise has to do with the signals occurring at the input and the output of the quantizer [242]. The concept was introduced while analyzing delta-sigma modulators in which the controller [240] generates the control signals as linear combinations of its input signals. In the analysis, the quantizer [242] was replaced by a linear model consisting of a gain element and an adder in which a signal called the quantization noise is injected. By doing so the modulator becomes linear; it is a linear filter with two input signals: d(k) and the quantization noise.

> The method has been used, with some success, to determine linear combinations for use in the controller [240], for which the modulator [202] is stable. However, for highorder modulators, the method tends to fail. Occasional saturation or reset of some filter stages [236] [238] seems to be necessary to assure the stability of the modulator [202]. In other words, to preserve stability, the controller [240] should have at least some nonlinearity built into it. Saturation and reset of the third and fourth filter stage [236] [238] is represented by the signals  $r_3(k)$  and  $r_4(k)$ , respectively.

> The dual-truncation principle, as it is described in U.S. Pat. No. 5,369,403, fails when the controller [240] is nonlinear. If the controller [240] is nonlinear, then the noise transfer function NTF(z) will be nonlinear. To obtain good

compensation for the quantization noise, the replica NTF of NTF(z) must have the same nonlinearities as those of NTF(z). It will be very difficult, if not impossible, to It is sometimes simpler or cheaper, but never a necessity, 45 implement such nonlinearities. As mentioned above, the consequence is large spikes in the output.

It is a key feature in the basic separator that the separation does not at all depend on how the controller is implemented. It may be linear, or it may be nonlinear; it does not matter. What matters is that the compensation signal remains bounded. Stability

Consider a baseband modulator in which all the filter stages [232] [234] [236] [238] are integrators. In the prior art, the signals  $r_3(k)$  and  $r_4(k)$  are used only to stabilize the modulator [202] in critical situations. FIG. 5.7 in the book, Delta-Sigma Data Converters; Theory, Design, and Simulation, shows a small amount of feedback from  $i_4$  (k) to r<sub>3</sub> (k) to produce a distribution of the modulator's zeros in the signal band. However, this variation does not compromise the following discussion. Consequently, during normal operation, the controller [240] assures the separator's [202] stability solely by means of v(k).

Stability essentially means that the output from each and all the filter stages [232] [234] [236] [238] remains bounded in magnitude. Controlling a cascade of N integrators from one end can be compared to backing a truck with N trailers;

10

each trailer's orientation is the output of the corresponding integrator. Obviously, stability is not easy to assure for high-order modulators/separators. With this analogy in hand, it can be understood that, to preserve stability, it, from time to time, may be required to do something drastic like 5 resetting an integrator or two (aligning of the trailers).

Stability can, however, be assured without resetting or saturating the first two filter stages [232] [234]. This will leave the operation of the basic separator [202] insensitive to nonlinearities in the controller [240].

Nonlinear Controllers

A main priority in the design of the basic separator [202] is to keep the magnitude of the compensation signal  $b_0(k)$  as low as possible. It is a priority because the chip area and the power consumption of the overall system will depend significantly on the maximum value of  $b_0(k)$ . Also, and of equal importance, because the system's [200] performance will be inversely proportional to the maximum value of  $b_0(k)$ .

A second main priority in the design of the separator [202] is not to reset or saturate the subsequent filter stages [236] [238] too often (otherwise they serve very little or no 20 purpose).

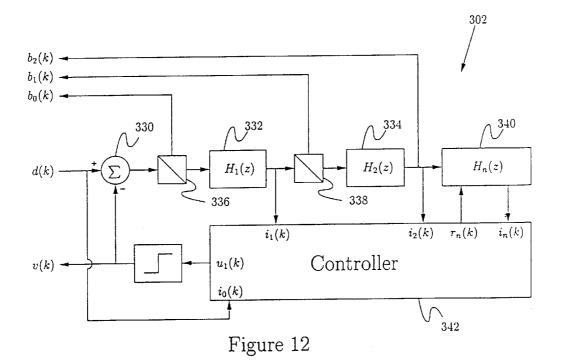

A Second Embodiment

FIG. 12 shows a separator [302] which is a variant of the basic separator [202]. It is intended for use as the separator [102] in a D/A converter system, implemented according to 25 the general structure [100]. It separates the digital input signal d(k) into a main digital signal v(k) and three digital compensation signals  $b_0(k)$ ,  $b_1(k)$ ,  $b_2(k)$ .

Description of the Second Embodiment

Only the separator [102], implemented as the separator 30 [302] shown in FIG. 12, will be discussed. The remaining part of the system [100] is considered to be implemented according to the prior art.